Cette unité est fortement pipeliné avec 7 étages au total.

(IFU = Instruction Fetch Unit, ID = Instruction Decode, RAT = Register Allocator and Translator et ROB = ReOrder Buffer)

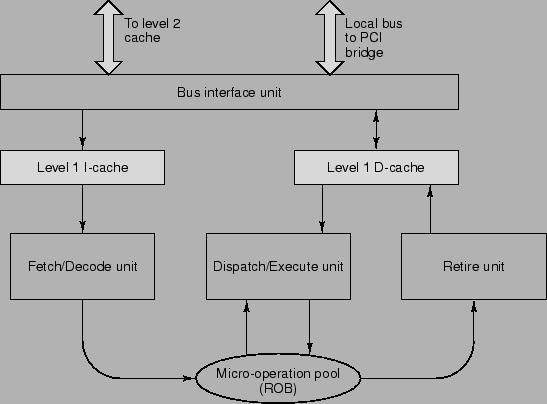

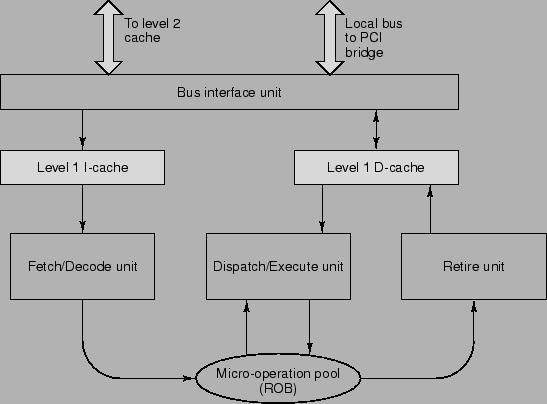

Quel est à votre avis le fonctionnement de la Fetch/Decode Unit ? Aidez vous du schéma précédent sachant que les instructions x86 décodées sont de longueur variables,

IFU0 : récuperation de la ligne dans le cache

IFU1 : détermination des frontières d'instructions (peut regarder

jusqu'a 30 instructions en avance)

IFU2 : alignement des instructions

et peuvent être traduite en une à quatre micro-instructions par trois unités de décodages.

ID0 : 3 decodeurs pour tranfformer l'instruction traitée

en micro-instruction de 118 bits

ID1 : mise en attente des micro-instructions et prédiction

de branchement

Un renommage final vers des registres internes est nécessaire pour éviter les interdépendances entre micro-instructions.

Les Pentium récents, avec leurs très longs pipelines, utilisent la prédiction de branchement pour savoir quelles instructions charger à l'avance et ainsi maintenir le pipeline remplis. Ne pas tenir compte de cette optimisation dans votre réponse.